The SAMD21 comes with a DPLL peripheral which allows scaling up an reference clock up from 48 to 96MHz variably. It can then be used as the source for the CLK_MAIN that runs the CPU.

This is a quick little guide on how to upscale the internal 8MHz clock to run the CPU clock at a higher frequency. This is particularly useful when needing performance and you are running the DFLL for USB clock recovery.

Currently ASF 3.19 and below are broken and do not allow configuring DPLL properly via only conf_clocks.h. The reason being you need to set the DPLL’s reference clock to a GCLK and system_clock_init fails to do so.

The first step to get the DPLL scaling your internal frequency is to configure a GCLK generator to output the internal 8MHZ oscillator. This can be any free available GCLK generator.

/* Configure GCLK generator 1 (DPLL Reference) */

# define CONF_CLOCK_GCLK_1_ENABLE true

# define CONF_CLOCK_GCLK_1_RUN_IN_STANDBY false

# define CONF_CLOCK_GCLK_1_CLOCK_SOURCE SYSTEM_CLOCK_SOURCE_OSC8M

# define CONF_CLOCK_GCLK_1_PRESCALER 8

# define CONF_CLOCK_GCLK_1_OUTPUT_ENABLE falseThe prescaler is set to 8 because the input to the DPLL must be 2MHz or lower. It is not rated for a higher input.

Now you must make the GCLK generator feed the DPLL GCLK channel

/* Set up GCLK */

struct system_gclk_chan_config gclk_chan_conf;

system_gclk_chan_get_config_defaults(&gclk_chan_conf);

gclk_chan_conf.source_generator = GCLK_GENERATOR_1;

system_gclk_chan_set_config(SYSCTRL_GCLK_ID_FDPLL, &gclk_chan_conf);

system_gclk_chan_enable(SYSCTRL_GCLK_ID_FDPLL);Now you can enable the DPLL to start running

struct system_clock_source_dpll_config config_dpll;

system_clock_source_dpll_get_config_defaults(&config_dpll);

config_dpll.reference_clock = SYSTEM_CLOCK_SOURCE_DPLL_REFERENCE_CLOCK_GCLK;

config_dpll.reference_divider = 1;

config_dpll.reference_frequency = 1000000;

config_dpll.output_frequency = 30000000;

system_clock_source_dpll_set_config(&config_dpll);reference_frequency is set to the output frequency of GCLK_GENERATOR_1 used above

output_frequency can be any value from 48MHz to 96Mhz. It can go as low as 30Mhz in practice but it’s not specced for that by Atmel.

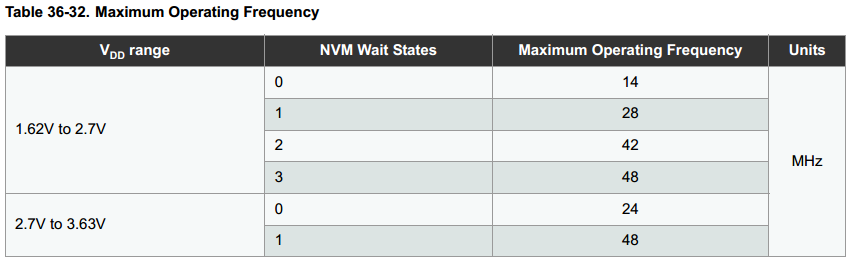

Next you must change the NVM controllers flash wait states according to the table in the SAMD21 datasheet

system_flash_set_waitstates(2);Enable the DPLL

system_clock_source_enable(SYSTEM_CLOCK_SOURCE_DPLL);And finally switch the GCLK generator 0 which is the CPU clock source over to the DPLL

struct system_gclk_gen_config config_gclock_gen;

system_gclk_gen_get_config_defaults(&config_gclock_gen);

config_gclock_gen.source_clock = SYSTEM_CLOCK_SOURCE_DPLL;

config_gclock_gen.division_factor = 1;

config_gclock_gen.output_enable = true;

system_gclk_gen_set_config(GCLK_GENERATOR_0, &config_gclock_gen);Lastly, it is good to check that DPLL is running

while(!system_clock_source_is_ready(SYSTEM_CLOCK_SOURCE_DPLL));